オーディオ D/A コンバーター

-

[Q0022] ・電源投入後、パワーダウン解除のシーケンスを教えてください。

-

A. ・電源投入後、PDNピンをL⇒Hとしてください。その場合Low状態を最低Reset時間(tPD)以上保持ください。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0023] ・起動時のクロック入力のタイミングを教えてください。

-

A. ・電源が投入された後であれば、どのタイミングでもクロック入力は可能です。但し、パワーダウン解除後にクロックを供給した時は、クロック供給されてから内部回路のタイミングがスタートし、アナログブロックがパワーアップします。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0024] ・クロックパワーダウンをサポートしているデバイスでMCLKおよびLRCKの供給が止まりパワーダウン状態になった場合、アナログ出力ピンの状態はどのようになりますか?

-

A. ・アナログ出力ピンは、Hi-zになります。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0025] ・クロックパワーダウンをサポートしているデバイスでパワーダウン後レジスタ設定値はクリアーされてdefault値になりますか?

-

A. ・レジスタ設定値は初期化されません。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0026] ・TDM256モードを使用する場合、fs44.1kHzの時マスタクロックには何MHzを供給すればよいですか?

-

A. ・11.2896MHz (256fs) 以上のマスタクロックを入力ください。詳細は個別のデバイスのデータシートを参照ください。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0027] ・デジタル入力信号のオーバーシュート、アンダーシュートのスペックはありますか?

-

A. ・スペックはありません。データシートの絶対最大定格VINDの値を超えた条件で使用した場合、デバイスが破壊することがあります。また、通常の動作は保証されません。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0028] ・デジタル入力ピンの入力容量はどれくらいですか?

-

A. ・入力容量は、5pF以下です。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0029] ・未使用のアナログ出力ピンの処理はどのようにすれば良いですか?

-

A. ・オープンとしてください。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0030] ・アナログ出力ピンの出力抵抗値はどれくらいですか?

-

A. ・出力抵抗値は、スペック、保証はしていません。実力値として1Ω以下と考えてください。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0031] ・VCOMピンに接続するコンデンサの容量を小さくした場合のメリット、デメリットを教えてください。

-

A. ・容量を小さくする場合 メリット:VCOMのスタートアップ時間が短くなり、動作状態に早くなります。 デメリット:1.ノイズの影響を受けやすくなります。 2.電源投入時のポップノイズが出力されます。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0032] ・VCOMピンの電圧が安定する前にデジタルデータを入力すると出力はどうなりますか?

-

A. ・VCOM電圧が安定する前にデジタルデータが入力された場合、アナログ波形が歪む事がありますので注意が必要です。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0033] ・アナログ特性の負荷抵抗 (Load Resistance) のスペックは、入力信号の周波数がfin 1KHzの時のみですか?

-

A. ・入力信号周波数20Hz ~ 20KHzでスペックしています。最終段のアンプが駆動できる負荷です。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0034] ・DACのアナログ出力端子からDC出力は可能ですか?

-

A. ・DC出力は仕様でスペックしていません。データシートでスペックしている測定帯域は20Hz ~ 20kHzです。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

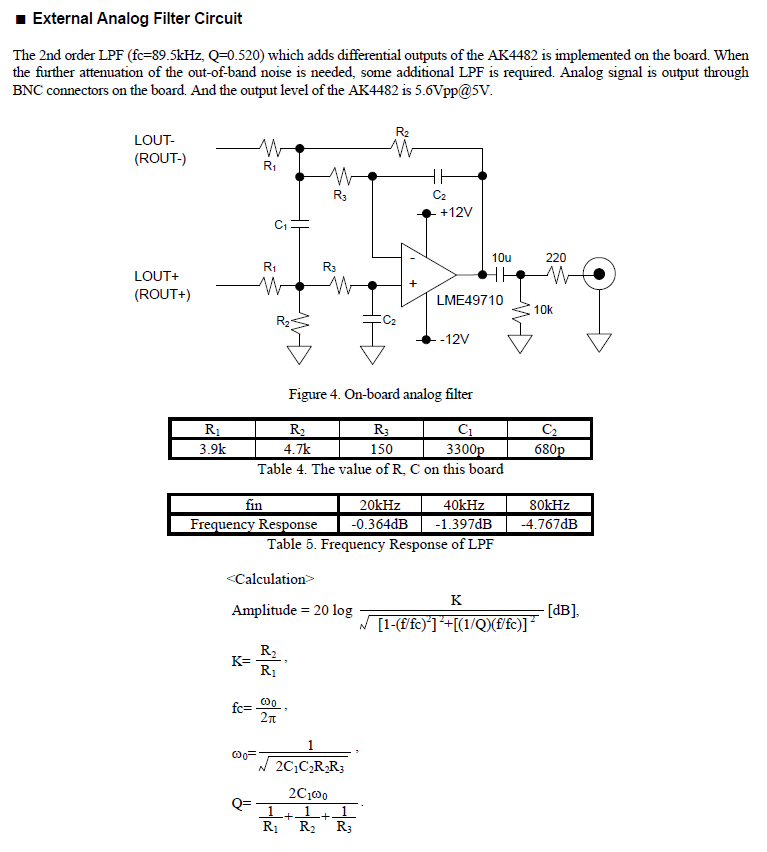

[Q0035] ・差動出力をシングルエンド変換する外部アナログフィルタ回路とその周波数特性の計算式を教えてください。

-

A. ・例えば AK4482 で示します。外部アナログフィルタ回路図、LPFの計算式は、データシートのアナログ出力及び評価ボードマニュアルに記載があります。

External Analog Filter Circuit お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0036] ・Group Delayの定義を教えてください。またmin/max値が無い理由を教えてください。

-

A. ・定義は、オーディオI/Fにデータがセットされてからアナログ出力ピンから出力されるまでの内部処理時間です。主に内部デジタルフィルタによる遅延ですのでバラツキはありません。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0037] ・入力チャンネルが複数ある場合、チャンネル間で位相差はありますか?

-

A. ・チャンネル間で位相差はありません。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0038] ・パワーダウン解除 (PDNピン: L→H) 後、レジスタアクセスを行うのに待ち時間を入れる必要はありますか?

-

A. ・パワーダウン解除後レジスタにアクセスが可能ですので、待ち時間を入れる必要はありません。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

[Q0039] ・HOSTから通信中にCSNを強制的にHとしてデータ通信を中断した場合、それまでに書き込んだデータはどうなりますか?

-

A. ・HOSTから通信中にCSNピンをL→Hした場合、コマンドはキャンセルされレジスタは更新されません。

お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。

-

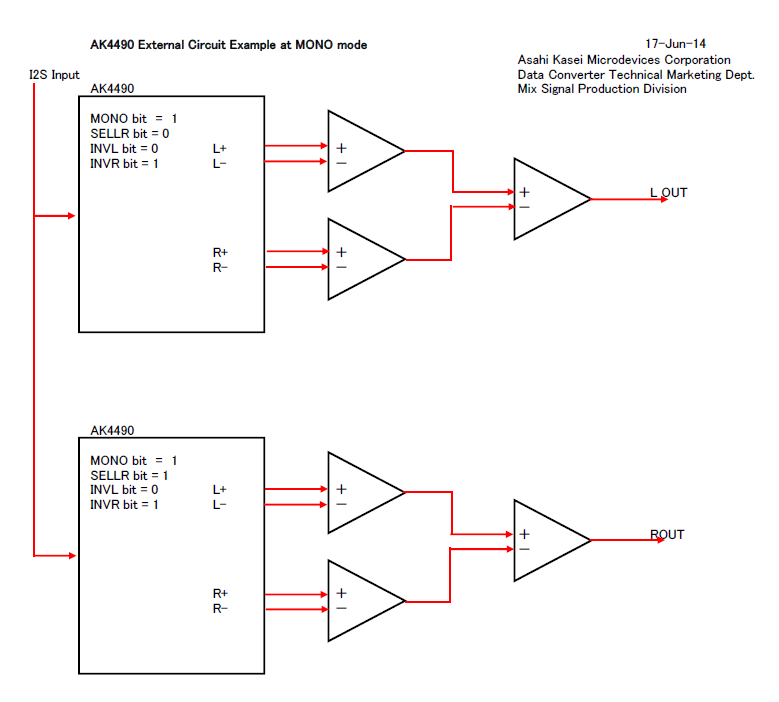

[Q0040] ・モノモードに設定した場合のレジスタ設定と外部ポストフィルタを教えてください。

-

A. ・AK4490 の回路模式図例は、こちらを参照ください。

AK4490 External Circuit Example お役に立ちましたか?YesNoご回答いただきありがとうございます。 みなさまのご意見を、WEBコンテンツの改善に反映させていただきます。